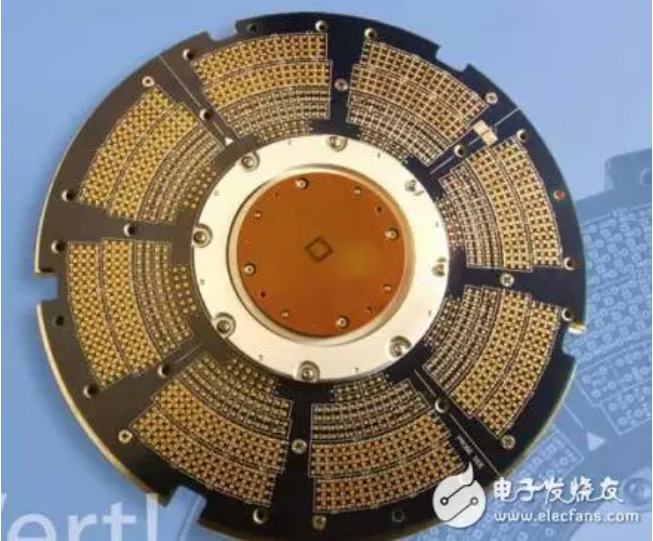

首先解释一下什么是CP和FT测试。CP是(Chip Probe)的缩写,指的是芯片在wafer的阶段,就通过探针卡扎到芯片管脚上对芯片进行性能及功能测试,有时候这道工序也被称作WS(Wafer Sort);而FT是Final Test的缩写,指的是芯片在封装完成以后进行的最终测试,只有通过测试的芯片才会被出货。

由于测试治具上的差异,CP和FT的不同点并不仅仅限于所处的工序阶段不同,两者在效率和功能覆盖上都有着明显的差异。

在绝大多数情况下,特别是在国内,我们目前在CP测试上选用的探针都还是悬臂针(也有叫环氧针的,因为针是用环氧树脂固定的缘故)。这种类型的针比较长,而且是悬空的,信号完整性控制上非常困难,所以一般数据的最高传输率只有100~400Mbps,高速信号的测试是几乎不可能的;另外,探针和pad的直接接触在电气性能上也有局限,容易产生漏电和接触电阻,这对于高精度的信号测量也会带来巨大的影响。所以,通常CP测试仅仅用于基本的连接测试和低速的数字电路测试。

当然,理论上在CP阶段也可以进行高速信号和高精度信号的测试,但这往往需要采用专业的高速探针方案,如垂直针/MEMS探针等技术,这会大大增加硬件的成本。多数情况下,这在经济角度上来说是不合算的。

那这样一来,我们还需不需要CP测试?或者在CP测试阶段如何对具体测试项目进行取舍呢?要回答这个问题,我们就必须对CP的目的有深刻的理解。那CP的目的究竟是什么呢?

首先,CP最大的目的就是确保在芯片封装前,尽可能地把坏的芯片筛选出来以节约封装费用。所以基于这个认识,在CP测试阶段,尽可能只选择那些对良率影响较大的测试项目,一些测试难度大,成本高但fail率不高的测试项目,完全可以放到FT阶段再测试。这些项目在CP阶段测试意义不大,只会增加测试的成本。要知道,增加一个复杂的高速或高精度模拟测试,不仅仅会增加治具的成本,还会增加测试机台的费率和增加测试时间。这些测试项目在FT阶段都是要测试的,所以没有必要放在CP阶段重复进行了。

其次,一些芯片的部分模组地管脚在封装的时候是不会引出来了,也就是说在FT阶段这些模组很难甚至无法测量。在这样的情况下,测试就必须在CP阶段进行。这也是必须进行CP测试的一个重要原因。

还有一种特殊情况,芯片的封装是SIP之类的特殊形式。一方面这种封装形式在FT阶段可测性较低,而且多芯片合封的情况下,整体良率受每颗die的良率影响较大,所以一般需要在封装前确保每颗die都是好品 (KGD: KnownGood Die)。这种情况下,往往无论多困难,都需要在CP阶段把所有测试项目都测一遍了。

所以,基于以上的认识,就比较容易在具体项目中判断CP测试项目的取舍了。简单而言:

1) 因为封装本身可能影响芯片的良率和特性,所以芯片所有可测测试项目都是必须在FT阶段测试一遍的。而CP阶段则是可选。

2) CP阶段原则上只测一些基本的DC,低速数字电路的功能,以及其它一些容易测试或者必须测试的项目。凡是在FT阶段可以测试,在CP阶段难于测试的项目,能不测就尽量不测。一些类似ADC的测试,在CP阶段可以只给几个DC电平,确认ADC能够基本工作。在FT阶段再确认具体的SNR/THD等指标。

3) 由于CP阶段的测试精度往往不够准确,可以适当放宽测试判断标准,只做初步筛选。精细严格的测试放到FT阶段。

4) 如果封装成本不大,且芯片本身良率已经比较高。可以考虑不做CP测试,或者CP阶段只做抽样测试,监督工艺。

5) 新的产品导入量产,应该先完成FT测试程序的开发核导入。在产品量产初期,FT远远比CP重要。等产品逐渐上量以后,可以再根据FT的实际情况,制定和开发CP测试。

本文转载自:电子发烧友网