想象一下这样一个场景: 你一大早起来赶早班飞机,昏昏沉沉地去洗澡时,昨天穿的衣服里装着的柔性传感小芯片发出洗衣提醒。早餐时,用平板大小的柔性显示器查看航班状态、新闻,浏览文本和视频。这时弹出医生发来的一条消息,提醒你贴上医用诊断贴剂,收拾好要带的药物。离开家时,地毯和墙纸里的微型传感器将一些家电改为待机模式。在机场,柔性电子客票指引你到登机口,机票、护照与视网膜扫描仪之间的无线连接使通关异常迅速。

虽然在日常生活用品中尚不能实现如此天衣无缝的集成运算,很大程度上是因为还没有便宜、超薄柔性的电子产品。但该技术已经越来越普及:射频识别(RFID)标签用于跟踪货物(且越来越多地用于跟踪宠物和人),汽车座椅中安装的柔性传感器会提醒父母去购物时不要把孩子遗忘在后座上,为电子书设计的可折叠显示屏正在研制中。这些具备内在柔性的产品可以大量生产,有的甚至可喷墨印刷,打造大屏幕显示器。

柔性芯片的主要材料是非硅有机和无机半导体,包括聚合物和金属氧化物半导体,因为成本是传统硅芯片的一小部分,使得柔性芯片成为刚性硅电路非常好的替代品,可以用以生产一些简单产品(例如光伏电池和电视屏幕)。但是,柔性电子产品在性能上不及传统方式制作的硅芯片。例如,2011年2月推出了第一款用有机半导体生产的微处理器,但4000个晶体管、8位逻辑电路运行速度低于10Hz的时钟频率。和1971年推出的英特尔404处理器(运行速度是100KHz)相比,慢了整整4个数量级。

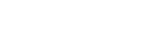

但有一种制造超薄硅芯片的技术,可能会带来许多高性能的柔性应用,包括显示器、传感器、无线接口、能源采集和穿戴式生物医学设备。硅是制造这种芯片的理想的半导体,因为它有序的结构确保了转换器良好的性能,比有机替代品快得多。

那么,如何才能两全其美呢?那就要将价格低廉的大型柔性电子产品与硅结合起来,这和最好的产品相比不仅性能相当,更重要的是更加轻薄。

硅芯片通常以一毫米厚的晶片为基础。 如此的厚度,使得晶片可以有足够的刚性和稳定性应付生产过程。将厚度缩小到100至300微米,硅片虽然可以保持一定的硬度,但必须小心处理。如果缩小到50和100微米之间,晶片可能会在自身重力作用下断裂。

奇怪的是,厚度小于50微米却是最佳状态:这时硅片更柔韧、更稳定。10微米以下,硅片甚至可达到光学透明,从而简化装配过程中芯片对准的难题,并可用作窗户和其他透明表面上的传感器。这些50微米以下的芯片是制造前文提到的薄膜电子设备的理想选择。它们能弯曲、扭转、卷起,而且与不锈钢一样坚硬,毕竟是由高性能晶体硅制成的。

正因为薄,所以堆叠性更强。由于三维集成电路的问世,这成为一个关键属性。随着芯片越来越复杂并且晶体管数目的增加,晶体管之间的金属连接变得越来越长,越来越复杂。堆叠的目的是通过硅穿孔技术垂直连接晶体管,使晶体管之间的距离缩短,从而增强性能。这正是闪存设计师们目前努力的方向。

但为了迎合正在开发的更小的晶体管,芯片需要更薄。如果一切顺利,这种芯片将能支持一系列全新的应用。与薄膜电器结合,超薄硅片可置于柔性基板上(通常是一个聚合箔,但也可以是纸或布),制成混合薄膜系统(SIF)设备。由此产生的超薄但高度集成的电路将有能力提供诊断疾病、设计家电程序、以及减轻清晨出行的困难。

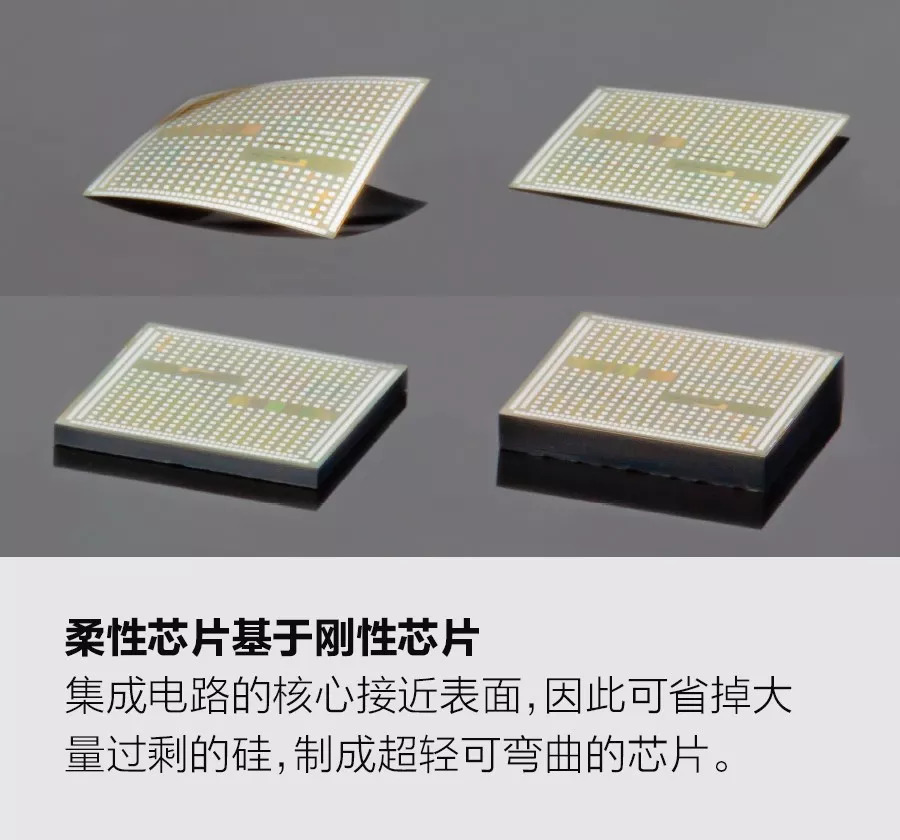

要得到超薄硅芯片并不简单。通常情况下,这些芯片是从比萨饼大小的大型超纯硅晶片切割而来的。电子线路只占磁盘顶端的5到10微米,也就是上面1%。其余部分只是作为坚实的衬底,经受住自动生产线的严格考验。

制造超薄芯片的最直接的方法就是磨去衬底。这一过程可以方便地在电路画好之后及晶片被切割成芯片之前完成,这样在加工过程中结实的衬底还是存在的。这种消减技术是国际半导体技术发展蓝图在2005年开始考虑晶元片薄化时提出的首个战略。

但是磨削和切割比较粗暴;会在晶片边缘处造成晶体缺陷和裂纹。虽然有保护晶片的变通方法,但厚度低于50微米时,这些步骤成本非常高。当晶片变薄,将其整体磨成均匀的厚度更加困难。芯片制造商必须保证超薄晶片的稳定性,只能暂时将其粘合到硅片或玻璃晶片(即载体)上;安装和拆卸这些载体的成本很高。

使芯片变薄的另一种方法是在较厚硅基板上的氧化物层上形成硅薄膜。有了这些硅晶绝缘体,SOI晶片(之所以如此命名,是因为氧化硅是绝佳的绝缘体),就能有选择地、均匀地将硅磨去。但SOI晶片的价格约为常规晶片的10倍,加上晶片研磨技术,处理过程需要额外的基板。除了这些技术困难外,两种消减技术都浪费99%的硅晶片。这就像面包师扔掉松饼的底层,只卖松脆的表层一样。

另一种方法是从最底层开始制造超薄芯片。这是一种颠覆性的解决办法,与半个世纪以来的芯片制造方法背道而驰,但随着各种应用需要的芯片越来越薄,减少浪费的层叠技术越来越理想。

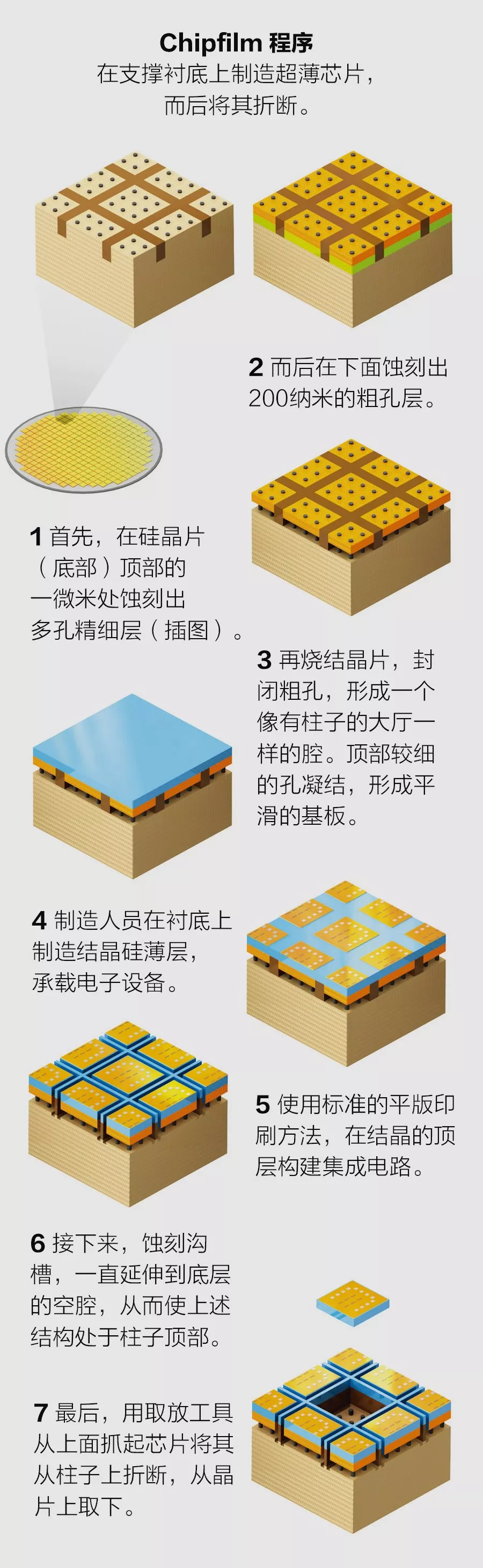

德国斯图加特微电子研究院开发了一种层叠技术,商品名为chipfilm。需要在有很多密封腔的基座上一层一层地结晶晶体硅。在这个方案中,将晶体硅层固定在一组小锚点上,确保基座在加工过程中足以支撑芯片,而完成的芯片又不难从晶片顶部折断下来。之后,我们还可以将大部分的硅作为衬底重新利用。

首先在固体晶片蚀刻出厚1微米的多孔硅层,然后在下面蚀刻出200纳米的粗孔硅层。接下来,在高温下将两层熔结起来,粗糙层的纳米孔融合,就像小肥皂泡合成大气泡一样,下面一层较粗的孔闭合,形成一个由垂直柱隔开的连续腔体。

表层作为结晶硅的种子,在晶片整个表面上结晶到所需的厚度。然后,芯片经过正常加工,即采用数百个步骤在芯片内和芯片上建立电子晶体管功能和金属互连。制作完成后,表层仍通过下层空腔内的柱子牢固地附着在较厚的硅晶片上。

为了从底座上将芯片折断,在芯片的边缘处蚀刻一条深深的沟槽,一直延伸到空腔。这样芯片只与支柱连接,由支柱支撑。然后创新地使用一款众所周知的取放工具。真空钳子通常用来抓取和传送芯片,而我们用它来抓组芯片拖拽,通过机械力折断垂直柱。有了沟槽,这并不难做到。

这时,支柱完成了使命,即在制造过程中保持芯片的完好,否则这么薄的芯片很容易在如此多的制作步骤中被损坏。由于芯片始终附着在某些东西上(基板或真空夹具),所以不会断裂或卷起。而后取放工具将每个芯片与其他薄膜组件堆叠或者放在柔性基板上。

取下芯片后, 可重复这一过程,对原始晶片进行抛光和修复。每重复一次,晶片就会变得更薄,这一过程可重复多次,直到晶片变得太薄。1毫米厚的晶片经过多次使用可降到400微米,其间形成约50层,每一层都能产生许多超薄芯片。残余的衬底就会丢掉,但使用这种技术,浪费的硅远远低于前面提到的消减技术。

由于消减技术可在芯片制造后实施,因此有时确实有逻辑优势。但经过完整加工后,硅片的价值约为原硅晶片的100倍,只有后期的磨削工艺成功率较高,这方面的优势才会显现。正如此前所提到的,随着芯片变薄,成功率也会不断下降。与此相反,层叠方法将大部分的薄化步骤移到开始阶段,这样即使出现任何失误,损坏的也只是未加工的晶片,而不是加工完成的珍贵晶片。此外,如果从底层开始制造芯片,芯片越薄,加工成本越低。但如果采用消减技术,情况恰恰相反。

把所有因素综合起来考虑,对于厚度超过100微米的芯片,消减技术的成本效益更高。但对于厚度小于30微米(3-D IC和较大的柔性SiF应用的理想厚度)的芯片,层叠方法的成本效益似乎更高。

引进新技术总是一个先有鸡还是先有蛋的问题:技术或应用,先有哪一个?对于超薄芯片的情况,业界如此致力于3-D IC的研究,在一定程度上回答了这个问题。为了继续微电子的小型化趋势,产业蓝图提出在2020年前将5到10微米厚的芯片用于3-D堆栈。芯片制造商有办法实现这一目标。

Chipfilm程序可将芯片厚度降至10微米,但尚无法进行大规模生产。原因是多方面的,例如,由于烧结过程会在种子上表面留下一些微小隆起,在表面上结晶的晶体硅可能存在瑕疵或堆垛层错。根据上部硅层厚度和孔隙率,优化烧结条件,可改善结晶硅和电路的质量。我们还在优化最后阶段的裂化技术(这个过程会损坏5%的芯片),进一步提高产量。

但即使在超薄芯片完成后,还要解决另外一些障碍。它们最具价值的柔韧性却使得它们很难贴在基板上。衬底和芯片之间可能产生气泡,就像保护膜和触摸屏之间形成的气泡一样。如果对芯片施加压力,这些气泡可能会使模具破裂。

按照3-D芯片蓝图,在克服这些难题的同时,竞相开发这类芯片将推动超薄芯片其他应用的发展。到2020年,电子纸平板电脑和其他高性能显示器市场将足够大,召唤超薄硅芯片的推出。如果芯片可以像金属箔载体一样超薄、柔韧,还可大大提高柔性芯片应用(如RFID、货币和安全文件的电子标签)的可靠性。

接下来就是真正令人难以置信的应用。由于超薄芯片可切割成各种形状,因此对医学领域的应用特别有用。圆芯片适用于视网膜植入物、微型内窥镜摄像头和诊断用药丸式摄影机。超薄柔韧的芯片甚至可能与人脑互动,收集或刺激神经系统活动,甚至可能增强脑力。这种互动非常困难,但有一点很明确:芯片必须超级薄,才不至于在与脑组织一起移动时造成伤害。

在这些应用的推出之前,有个能提醒洗衣的芯片我已经很高兴了。

本文转载自:半导体行业观察